Page 1 :

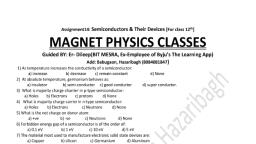

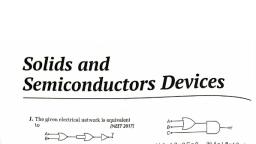

e basic materi, re elemental (Si, Ge) wean en eu, 2, Intrinsic semiconductor, These are Pure, and holes., 3. Extrinsic semiconduc;, specific impurities, , ed in the present solid state electronic devices like diode, transistor, 88 well as compound (GaAs, Cds etc.), , Semiconducting materials. The electrical conduction is by means of mobile electrons, ictors, These are obtained by adding the pure semiconductor material with small amount of certain, with valency different from that of the atoms of parent material,, , adding impurity to pure semiconductor material is called doping., , Semiconductor! Thi, , 5, Conductivity of a pure The conductivity of a pure semiconductor is given by, , eis charge on the electron or hole,, o=e(n, B+ ny py), , n, and n,, are electron and hole density,, H, and yi, are electrons and holes mobility, , where, , 6. N-type semiconductor. N-type semiconductor of Si or Ge is obtained by doping with pentavalent atoms (donors) like As, Sb,, Petc. Here n, >> n,., , 7, P-type semiconductor., , P-type semiconductor of Si or Ge is obtained by doping with trivalent atom (acceptors) like B, Al, In, etc. Here n,, >> n,., , iece of III group metal like In (Indium) is placed over n-Ge or n-Si and melted, the lower portion, 8 areata mapa ne ‘th the n-semiconductor and converts its top layer into p-layer to form p-n junction., of molten, ico! i i i + =, iconductor diode is a p-n junction with metallic contact, ‘. saat see gt a apelin of an external voltage. A p-n junction diode is Pp n, Provided at the e:, Tepresented as Figure 14.1., , Figure 14.1, ea tralized acceptor and donor ion across a P-n junction is called depletion region., ion containing unneut conor, , '®. Depletion region. The regio ic field between the acceptor and donor ions is called the barrier. The difference of potential from, 11. Potential barrier. The yee other side is called potential barrier., , Sne.side'of the harer jiasing of p-n junction. A p-n junction is said to be fo, , 12. Forward biasing and never U nregions. A p-n junction is said to be reverse biased, , higher potential with respec, , with respect to n region., , ode as a rectifier. A rectifier is a circuit which converts an alternating current (a.c,) into direct current, 13, lication of junction diode as 1 diodes are used., , ia For this purpose one, two or pd is used, the output is d.c. but it is fluct, , . a Half wave rectifier. When a two diodes D, and D, are used in such a wat, , In this, , (i) Full wave rect and vice-versa. Although we get full wave rectified but, is in reverse bit, , Tward biased if p region is maintained at, ff p region is maintained at lower potential, , ‘uating, although we get half wave rectified., , y that when D, is in forward biased then D,, , the output is fluctuating d.c., , , , Scanned with CamScanner

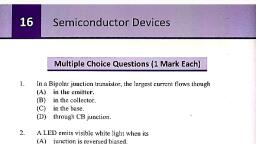

Page 2 :

BA. Special Purpose p-n junction diodes, There are some special purpose diodes, which are developed for different applications,, Example : (i) Zener diode (i) Photodiode _—_(ifi) Light emitting diodes (LED) _(iv) Solar cell, , 15. Zener diode. Zener diode is a special purpose diode, which can operate in reverse breakdown voltage region continuously, without getting damaged. A zener diode can be used as a voltage regulator., , 16. Junction transistor. Transistor is an n-p-n ot p-n-p junction diode. The central block is called base while the other electrodes, are emitter and collectors. The emitter-base junction is forward biased while collector base junction is reverse biased., , 17. Transistor circuit configuration. The transistor can be connected in either of the following configurations :, () Common Emitter (CE), (i) Common Base (CB) (ii) Common Collector (CC)., , 18. Transistor parameters for CE-configuration. The important transistor parameters for CE-configuration are;, , () Input resistance, R, = (S=) (ii) Output resistance, Ry = (4), By ch,, , (ii) Current amplification factor, BL. = (25) and By. = ic, Als )y Ip, , 19. Transistor as a device. The transistor can be used as a device application depending on the configuration used, the biasing of, , the E-B and B-C junction and the operating region namely cut off, active region and saturation. Thus transistor can be used, as:, , (i) a switch (i) an amplifier, , 20. Transistor as an amplifier (CE-configuration), , , , () Input signal voltage (@) V, =I Rg (b) V,= r Aly, (i) Output signal voltage (@) Vo =e Re (BD) Vg = AVg: = - Ry, Aly, (ii) Voltage gain (A,) of the amplifier is, Vo _ IcR, R, AV, Bac-R, (a) = 2= °C -g/ "Cc 'b) Ay = | SSE} = — Pact, Ay Vv; IpRp B Rp (B) Ay rAlp r, ( Ay= a +» where [Ap is power gain, and B,, is current gain.], , 21. Transistor as an oscillator. The frequency of the oscillations produced is given by,, , fe, , TE. -». Where [C is capacitor and L is inductor], , , , 22. Digital signal. A signal which has only two levels of voltage and does not vary continuously with time, is called digital signal., The two levels of a digital signal are represented as 0 or 1., , 23. Logic gate. A digital circuit which works according to some logical relationship between iny, logic gate. The five common logic gates used are ‘NOT, AND, OR, NAND and NOR’,, , 24. Truth table. It is a table, which shows all the possible input combinations and the corres;, gate. Truth tables help to understand the behaviour of logic gates., , 25. NOT gate This is the most basic gate, with one input and one output. It produces as 1 output if the input is 0 and vice, put and output voltage is called a, , ponding output combination for a logic, , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , versa., The logic symbol and truth table are shown in Figure 14.2, Input Output, A vi iA ony., Q 1, 1, Logic symbol 0, Figure 14.2 Truth Table, 26. OR gate. An OR gate has two or more inputs with one output. The output Y is 1 when either input A or input B or both are 1., The logic symbol and truth table are shown in Figure 14.3, Input _ Output, A A B. Yy, 0 0 0, iv 0 i i, 1 0 1, B } 0, Logic symbol Truth Table, , Figure 14.3, , , , Scanned with CamScanner

Page 3 :

gate. An AND gat, , a , e has tw, 1. The logic symbol and truth er More inputs and, ‘able are shown in Figueia4 The output Y is 1 only when input A and input B are both, , , , , , , , , , | A, | Input Output, | A B y, B x 0 0 0, , 0 1 0, Logic symbol 1 0 0, | 1 1 1, | NOR gate. It has two or more iny Figure 14.4 Truth Table, , puts and o;, me output. A NOT operation applied after OR gate gives a NOR gate. Its output Y is 1 only, , when both inputs A and B, are 0. ‘i, The logic symbol and truth table are shown in Figure 14.5, , , , , , , , , , , , , , , , , , A Input Output, Y A B Y, B 0 0 1, 0 1 0, Logie eymba rf eo] 3 |, Truth Table, Figure 14.5, , 29. a - It has two or more inputs and one output. A NOT operation applied after AND gate gives a NAND gate. Its output ¥ is, 0 only when both inputs A and B are 1. The logic symbol and truth tables are shown in Figure 14.6, , , , , , , , , , , , , , , , , , A Input i Output, A B 5 Vos, Y 0 0 1, Bom 0 1 1, 1 0 1, 1 L 0, , Logic symbol, Truth Table, , Figure 14.6, , NAND gates are considered as universal gates. We can obtain all the gates like NOT, OR, AN, , Important tips. Both NOR and, by using only NOR or NAND gates., 30. Integrated circuits. Many logical gates oF, Integrated circus 2° = st dogic gates < 10), in ;, a os geal Integration — ve (0B 00) °, . _ LSI (logic =, (ii) Large Scale integration ~ 15) er ogic gates > 1000), , tion Lm very Large Scale Intesrau?, , circuits are integrated in one single Chip. These are known as Integrated Circuits (1, , , , , , , , , , , , , , , , , , , , , , , , , , <i Unit Dimensions, S (simen) (M“L3T3A2], , C i vit m vist [ML3T4A7], , onduct mv! st [ML°T4A7), , A ms, , Mobility of oe No unit Dimensionless, Mobility orl tion factor A, No unit Dimensionless, Current @! ifier *, voltage gain of the amplifi, , , , Scanned with CamScanner

Page 4 :

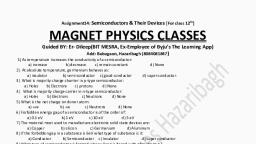

Very Short Answer Type Questions (VSAJ, (1 Mark), 2008, , 1. State the reason, why GaAs is most commonly, used in making of a solar cell. (All India), GaAs is most commonly used in making of a solar cell because :, , () It has high optical absorption (~ 104 cm7}) ., (ii) It has high electrical conductivity., 2. Why should a photodiode be operated at a, reverse bias? (All India), As fractional change in minority charge carriers is, more than the fractional change in majority, charge carriers, the variation in reverse saturation, current is more prominent., , 2009, 3. Give the logic symbol of NOR gate. (All India), Ans., , , , Ans,, , Ans., , , , . = >— Y= A+B represents a NOR gate., , 4. Give the logic symbol of NAND gate. (All India), , Ans. A oa, <n, , 5. Give the logic symbol of AND gate.(All India), Ans. ‘“, —, 2011, , 6. In a transistor, doping level in base is increased, slightly. How will it affect (i) collector current, and (ii) base current? (Delhi), , Ans. Increasing base doping level will decrease base, resistance and hence increasing base current,, which results in a decrease in collector current., , 7. What happens to the width of depletion layer of, , a p-n junction when it is (i) forward biased,, , (ii) reverse biased? (Delhi), , (i) In forward biased, the width of depletion, layer of a p-n junction decreases., , (ii) In reverse biased, the width of depletion, layer of a p-1 junction increases., , , , , , , , Ans., , 2012, , 8. What i :, y petype intrinsic semicondu, , s the difference between an 1-type and a, ctor?(Comptt. Delhi), , , , , , , , , Ans. Tantype semiconductor | p-type semiconductop, The electron density The hole density 7) is, (n,)_ is much greater much greater than the, than the hole density electron density (n,),, (iy), te, Ny >> Mie Le, Ny >> Ne9, The figure shows the I(mA), V-I characteristics of a, semiconductor device. Reverse bias|, Identify this device. Vz Forward bias, Explain briefly, using the yy, necessary circuit diagram,, how this device is used as, a voltage regulator. (uA), (Comptt. Delhi), Ans. Refer to Q. 64, Page 313, 10. How does the depletion region of a p-n junction, diode get affected under reverse bias?, (Comptt. Delhi), Ans. Depletion region widens under reverse bias., 11. How does the width of depletion region of a, p-n junction diode change under forward bias?, (Comptt. Delhi), Ans, The width of depletion region of a p-n junction, diode is small under forward bias., 2013, 12. The graph shown in the, figure represents a plot B, of current versus voltage __, for a_ given semi- =, conductor. Identify the = ¢, region, ifany,over which 3 A, the semi-conductor has a, negative resistance, ° Voltage (V), (All India), Ans. Between the region B and C, the semiconductor, has a negative resistance., 13. Write the truth table for, , a NAND gate as shown, in the figure., (Comptt. All India), , — fo, , Ans. Truth table for NAND gate, , , , , , , , , , , , A B Y, 0 0 1, 0 1 1, 1 0 1, 1 1 0, , , , , , Scanned with CamScanner

Page 5 :

‘i what is the function of a Photodiode?, (Comptt, All Indi, iode i eee . ia), we A hotodiode isa ‘Special Purpose p-n jancilon, "diode ek with a transparent window to, allow light to fall on diode. It is operate,, toate Bins Operated under, 5 write the truth table for, i - NOT gate connected 4 *——~ Y, as shown in the figure., , (Cc s, ns. Truth Table omptt. All India), , , , , , , , , , lel 4 | Bl aa [AG an, | fo] o} 1 1 1 0, ito} 1 1 0 1 0, , 1] 0 0 1 1 0, , 1 4 4 0 0 0 1, , , , , , , , , , , , , , This combination acts as AND gate., 46. Write the truth table of a two point input NAND, , , , , , , , , , , , , , , , gate. (Comptt. All India), Ans. Truth Table:, A B Y = AB, 0 0 1, 0 1 1, 1 0 ad, 1 1 0, 2014 i si. with, 7 jati f resistivity © i wi, 17. Show variation of res y (Delhi), , temperature in a graph., Ans., , t, &, , , , , , a, © Temperature (1), , < jati f current versus, 18. Plot a graph showing variation 8 (Delhi), , voltage for the material GaAsI, , , , , , Ans. A Graph showing variation of, current — versus, voltage for GaAs, , v_ (open circuit voltage), , short circult current, , |, fg o acgie, , = f N. f, 19. Draw the logic symbol © (Compt. All India), its Truth Table., , , , Ans. Symbol of NAND Gate, ‘Truth table, , , , 2016 20. Identify the logic gate, when both of its inputs, , whose output equals 1, are 0 each., (Comptt. Delhi), , Ans. NAND gate oF NOR gate., , 2017, , 21. Name the, characteristics are, , whose I-V, , junction diode eli), , drawn below:, , I, , Ans. Solar cell, , Short Answer Tyne Questions-1 (SA-1), (2 Marks), , 2008, 22. Distinguish between an intrinsic semiconductor, and p-type semiconductor. Give reason, why, a, p-type semiconductor crystal is electrically, neutral although 1), >> 1,? (Delhi), , (i) Intrinsic p-type, semiconductor semiconductor, , , , Ans., , , , 1.) The ure, , semiconductors (G6 or Si) in which the, electrical conductivity is totally, governed by electrons thermally, excited from the, valence bond to the, conduction bond are, called intrinsic, semiconductors., 2.|They have equal, number of densities, of free electrons and, holes i.e. n, = Ny., , tetravent — semiconductor of Si or Ge, doped with trivalent, impurity atoms of B, Al, or In is called a p-type, semiconductor., , It has more density of, holes than density of, free electrons i.e., Ny >> New, , , , , , , , , , , , , , ak, , , , (ii) In a p-type semiconductor, the trivalent, impurity atom shares its three valence, electrons with the three tetravalent host, , Scanned with CamScanner