Page 1 :

>, , Chapter, , 8051 INSTRUCTION SET, Ss, , A processor performs a job by reading and executing the, instructions written in its program memory. This set of instruction, ot, perform a specific job is called a program. Each processors has its own a |, instructions. 8051 has 111 different types of instructions with 241 total Numbers, instructions opcodes. These instructions are one byte, two byte and three byte ine, An instruction may not have any operand or can have one or maximum i, operands. Each instruction is normally made up of three parts : * |, , part 1 part 2 part 3, Destination operand Source operand |, , , , , , mnemonic, , , , , , , , part 1, the instruction mnemonic tells the processor the operation it has to, , perform like ADD, SUB tract, Data MOVE etc., part 2, the destination operand is an operand or data address that specifics the, , destination for the data., part 3, the source operand is an operand or data address and specifies the source, , for the data., 8051 Instruction set can be divided into following five types :, , () Data Transfer Instructions, , (ii) Arithmetic Instructions, , (ii) Logical Instructions, , (iv) Boolean Instructions, , (v) Program Branching Instructions., , 7.1. DATA TRANSFER INSTRUCTIONS, ed to copy a data from one location to another., , Data transfer instructions are us', The location may be a register or a memory location or an I/O port. The following, , five types of opcodes are used to move data :, , () MOV, (ij) MOVX, , 148

Page 3 :

ON, , 150 ISHAN'S Programmable Logic Controllers and Mierg, , (iv) Register-Indirect Addressing Mode, (v) Indexed Addressing Mode, , ta,, , 7.1.3 Register Addressing Mode, , In register addressing mode, operand lies in a register and is Specified bY ng, of the register. In 8051, Registers A, DPTR and RO to R7 may be named ag A ae, opcode mnemonic., , Example :, , MOV A, R2 : Moves the contents of source register R2 to destination register 4, In this instruction, both the operands (source and destination) are specif;, register addressing mode. Contents of register R2 remains unchanged., , MOV R7, A: Moves the contents of source register A to register R7 while the, contents of register A remains unchanged., , ied Using, , 7.1.4 Immediate Addressing Mode, , In immediate addressing mode, the operand is a part of the instruction itself, There is no need to specify register or memory location for operand. Immediate, addressing mode can be used for source operand only, not for destination operand. In, an instruction, only one operand can be specified using immediate addressing mode., , MOV A, #4F H ; Loads 4FH into A, MOV R1,#18H ; Loads 18 H into R1, MOV DPTR, #3982H_ ; Loads 16 bit data 3982H into 16-bit register DPTR., , # symbol is used to indicate immediate addressing mode,, , 7.1.5 Direct Addressing Mode, , In direct addressing mode, the address of the memory location, where operand, lies is directly specified in the instruction. In 8051, if there are two operands, then, both operands also can be specified by direct addressing mode. Only internal RAM, (00H to 7FH) and SFRs (80 H to FFH) with 8-bit address can be specified using, direct addressing mode not the external data memory., , Example : ., , MOV RO, 23H : Copies the contents of RAM location 23H into register Ro,, , MOV A, 81 H : Copies the contents of location 81 H ie. SP special function, register into register A. a, , MOV DOH, R7: Copies the contents of register R7 into location With address, DOH i.e. PSW register.

Page 4 :

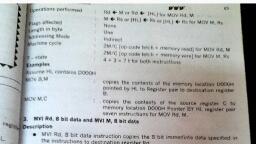

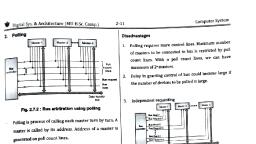

>, , Set, ruction ;, 41s H, 03H ; Copies the contents of RAM location 03H (Register R3 of, , into location with address 8AH i.e, TLO Timer 0 register., , 151, , wee irect Addressing Mod, ister Indirect Addressing Mode, , : gister indirect addressing mode, a register is specified which contains the, M “t the memory location where operand lies. If the operand is in internal, ° R then only registers RO and R1 can be used to specify the 8-bit, , sade r in SF, ° of the memory location. The sign @ is prefixed RO/R1 to indicate register, s, , si? addressing mode :, in yov @ RO : Copy the contents of internal data memory location whose, , jaress i8 held by RO, into A., Mov @ Ri, ‘A: Copy the contents of A into memory location (internal) whose, , adress is held by Rl., al Note that command MOV A, RO copies the contents of RO into A, instead of the, , sotents of memory location pointed by RO., , Ifthe operand is in external data memory, then registers RO and R1 can be used, tn specify the 16-bit address of the memory location from 0000H to 0OFFH, i.e. RO, and R1 specify only lower byte of the address and upper byte is 00H. 16-bit register, DPTR can also be used to specify the 16 bit address of external data memory location, fom 0000H to FFFFH. MOVX command is used for this purpose., , External Data RAM, , , , , , , , , , , , , , , , , , 8051, Data Bi, sl Data Register, MOVX @Ri —_0000-00FFH, Memory, Address, MOVX @ DPTR 0000-FFFFH Register, , , , , , , , , , , , , , , , , , , , , , Fig. 7.1 : External Data Memory Access, , ieee A, @ Rl : Copies the contents of external data memory location, whose, sion byte is held by R1 and upper byte is OOH, into register A., hts add @RO,A: Copies the contents of A into external data memory location,, ‘ess lower byte is held by RO and upper byte is 00H.

Page 5 :

ON, , 152 ISHAN'S Programmable Logic Controllers ang Mictooy, , Nr, MOVX A, @ DPTR : Copies the contents of external data memory In Shy, pointed by DPTR (16 bit) into A. Mig, MOVX @ DPTR, A : Copies the contents of A into external daty men, oy, , location pointed by register DPTR. oo, Note : Symbol @ is prefixed with RO, R1 and DPTR to indicate register ing;, , I z I, addressing mode. Only register “A” can be used to exchange 8-bit data with exten, data memory and the command used is MOVX. ‘l, , 7.1.7 Indexed Addressing Mode, , In Indexed Addressing mode, the contents of two registers are added to form th, 16-bit address of the memory location where operand lies. In 8051, only Progran, memory can be accessed using indexed addressing mode. This mode is widely Used jy, accessing data elements of look-up table enteries. MOVC command is used for this, , purpose and contents of ROM can be transferred to accumulator (A) only., InternaV/External ROM, , , , 8051, , , , , , , , , , , , , , , , , , , , , , , , , , , , , Data, A Data Register, Address Memory, pees Address, o MOVC A, @A+DPTR Register, MOVC A, @A+PC, , , , , , Fig. 7.2 : ROM Access for Code Data, , MOVC A, @A + DPTR : Moves the 8-bit contents of program memory location,, whose address is obtained by adding contents of A and DPTR register, into register A, , MOVC A, @ A + PC: Moves the 8-bit contents of program memory location,, whose address is obtained by adding contents of A and PC registers, into register A., Here PC is incremented first to point to next instruction before added to A to get, , the address., , 7.1.8 MOVX Instruction, , MOVkX instruction is used for external data transfers. This instruction transfers, data between CPU register A and external data memory or 1/0 devices. To specify, external memory, only register indirect addressing mode ig available Memory, location cannot be specified using direct addressing mode or indexed addressing, mode. If a data from any SFR other than A or any internal RAM location is to be